- 说明

- 点击数:2454

Xilinx的成本优化产品组合Zynq和Artix UltraScale+

如果你做FPGA,扩大份额并进一步进入市场的一种方法是发布一种新的COP或称作成本优化产品组合(cost-optimized portfolio)。这就是Xilinx(赛灵思)正在和TSMC(台积电)一起做的16nm Zynq和Artix UltraScale+系列产品的事情,这些产品给成本优化市场带来了更高的性能,更低的功耗以及更小的封装。

Xilinx Zynq和Artix UltraScale+成本优化战略

现在,Xilinx有了新的Zynq和Artix UltraScale+产品组合,这些产品是16nm UltraScale+器件(不是新的Xilinx Versal ACAP),但是是专门为成本优化和低功耗应用而设计的。

- 说明

- 点击数:2052

RISC-V是加州大学伯克利分校(University of California at Berkeley,以下简称UCB)设计并发布的一种开源指令集架构,其目标是成为指令集架构领域的Linux,应用覆盖IoT(Internet of Things)设备、桌面计算机、高性能计算机等众多领域。其产生是因为UCB的研究人员在研究指令集架构的过程中,发现当前指令集架构存在如下问题。

- 绝大多数指令集架构都是受专利保护的,比如:x86、MIPS、Alpha,使用这些架构需要授权,限制了竞争的同时也扼制了创新。

- 当前的指令集架构都比较复杂,不适合学术研究,而且很多复杂性是因为一些糟糕的设计或者背负历史包袱所带来的。

- 当前的指令集架构都是针对某一领域的,比如:x86主要是面向服务器、ARM主要是面向移动终端,为此对应的指令集架构针对该领域做了大量的领域特定优化,缺乏一个统一的架构可以适用多个领域。

- 商业的指令集架构容易受企业发展状况的影响,比如:Alpha架构就随着DEC公司的被收购而几近消失。

- 当前已有的各种指令集架构不便于针对特定的应用进行自定义扩展。

为此,UCB的研究人员Krste Asanovic、Andrew Waterman、Yunsup Lee决定设计一种新的指令级架构,并决定以BSD授权的方式开源,希望借此可以有更多创新的处理器产生、有更多的处理器开源,并以此降低电子产品成本。

RISC-V自2014年正式发布以来,受到了包括谷歌、IBM、Oracle等在内的众多企业以及包括剑桥大学、苏黎世联邦理工大学、印度理工学院、中国科学院在内的众多知名学府与研究机构的关注和参与,围绕RISC-V的生态环境逐渐完善,并涌现了众多开源处理器及SoC采用RISC-V架构,这些处理器既有标量处理器,也有超标量处理器,既有单核处理器,也有多核处理器,本文接下来将简单介绍RISC-V架构的基本设计,随后将详细描述目前采用RISC-V架构的开源处理器与SoC。

下载地址

- 说明

- 点击数:2445

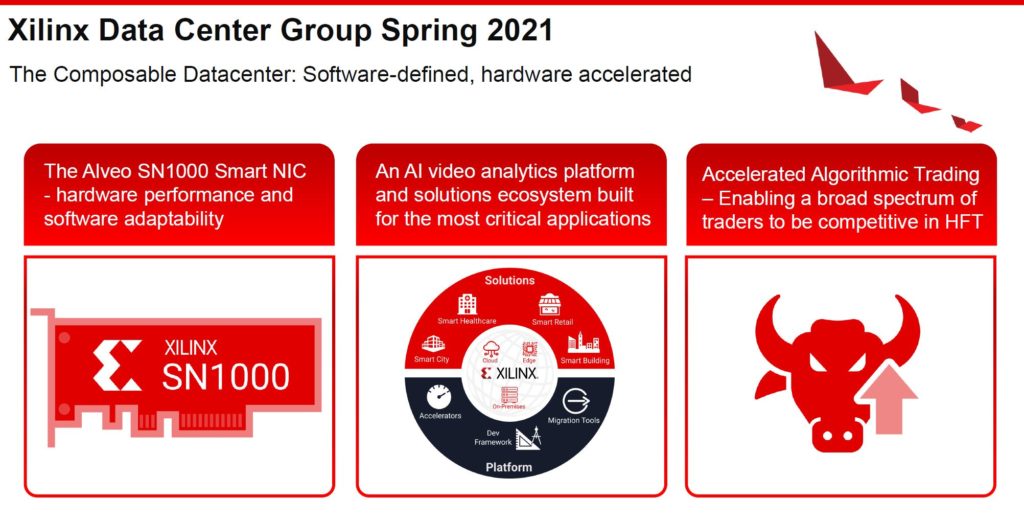

本周,Xilinx(赛灵思)数据中心集团发布了一些新技术,在重点分析被称为Xilinx Alveo SN1000的新型100GbE智能网卡(SmartNIC)前,我们先介绍一些更广泛的产品组合的更新。

Xilinx数据中心集团2021年春季公告

Xilinx数据中心集团2021年春季更新主要发布了三个公告。首先是前面提到的Alveo SN1000,接下来是被称为“Smart World”的AI视频分析平台,最后,Xilinx新出了一个加速算法交易解决方案。

有一个重点,可能是影响最大的一个,甚至没有出现在Xilinx更新的幻灯片上,Xilinx将会有一个新的App Store。Xilinx正在开拓一个新的市场,如果你在Xilinx FPGA上开发IP模块或解决方案,你可以将其放在Xilinx公司的App Store中,那些购买了Xilinx FPGA的人可以进入App Store,然后购买IP并用在其硬件上,而无需自己从头开发这个IP,从而节省了整个开发周期的时间。

- 说明

- 点击数:2082

摘要:

现场可编程逻辑门阵列(FPGA)在航电系统领域广泛应用,但是采用JTAG方式更新FPGA程序,效率低下,易受设备环境限制而缺乏灵活性,已经难以满足工程应用的需求。提出了一种实现FPGA程序远程更新的方案,该方案采用RapidIO总线,以软件异构的方式,构建在线更新实时通信链路。通过以太网下发镜像升级文件,经SRIO交换网络传送至FPGA节点,写入FLASH配置空间,实现FPGA程序的远程更新。经过测试,验证了设计的正确性和可行性,并有效地提高了FPGA程序更新的速度。

下载地址

基于RapidIO的FPGA远程更新系统设计与实现

© 2026 VxWorks Club