关于复位

数字电路中,电路通过复位来启动,复位犹如数字电路的“起搏器”,主要有下面三种方式:

- 无复位:天生就强壮着,上电就启动

- 异步复位:好心人路过,随便踢了一脚,起搏了,这完全没有心理准备,随时都有可能复活啊

- 同步复位:专业救援队,手按住胸口,不起博按住不放啊。直到听到“砰砰”声才离开,非常关键,必须要按住一会会

没见过这样写代码的,竟然没有复位,老师都说数字电路离不开复位的,没有复位,寄存器怎么赋初值啊?没有确定的初值,这电路怎么工作呢?

其实,不用担心,FPGA上电之后,寄存器初始值默认为“0”,当然,也可以人为的赋初值。下面为无复位的代码:

reg [7:0] my_register;

always @(posedge clk) begin

my_register <= data_in;

end

如果没有复位信号,省了很多资源,编译和布线时间也缩短不少,如果规模很大,对提高设计整体性能也是有帮助的。但是在数字电路设计中,我们很少不用复位电路。到是我们经常利用FPGA这个特性,自己产生内部复位电路。

异步复位电路描述:在always语句中添加复位信号在敏感量列表中,即可实现异步复位。

reg [7:0] my_register;

always @(posedge clk, posedge rst) begin

if(rst)

my_register <= 8’h0;

else

my_register <= data_in;

end

异步复位对复位信号要求很严格的,不然随便一个毛刺就会把电路给复位掉的。

另外,异步复位信号依赖于FPGA内部的传导延时,因此,在微小的电压或温度差异下,设计都有可能输出错误,设计的可移植性也很差。上面不是说了嘛,这随便一脚提过来,有时候能感觉到,有时候感觉不到啊。冬天穿个大棉袄,就得使个大劲才能提醒。

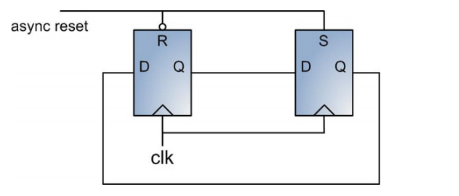

正因为对不同寄存器延迟是不同的,所以容易引发间断性设计问题。怎么理解呢?

如图所示,2 bit的移位寄存器组成一个环,复位后,左边寄存器清零,右边寄存器置位,而且都在同一上升沿触发,所以,如果左边寄存器上升沿来的时候,复位信号已经释放掉了,但是右边寄存器还处于复位状态,这个时候数据就错误。

异步复位不依赖于时钟。所以如果时钟是外部输入的,而且时钟有可能丢失,例如处于省电模式时,只能使用异步复位。

另外一个优势是设计更快的物理实现。相对于同步复位,异步复位有更宽松的时序约束。从而布局布线工具使用更少的时间便可达到约束条件。

同步复位就是非常专业,不留一点马虎,和他的名字一样,只在时钟的有效沿发生,所以一个有效的同步信号,至少要维持一个时钟周期(把你叫不醒,是不会停的)。由于仅仅在时钟的有效沿有效,所以可以滤除复位信号上的毛刺,电路可靠性好很多。

reg [7:0] my_register;

always @(posedge clk) begin

if(rst)

my_register <= 8’h0;

else

my_register <= data_in;

end

所以,总结一下。其优点是“弥补了异步复位的所有缺点”,其缺点是“没有异步复位的优点“”。这个总结够简单吧。

我们熟悉了3种复位方式,了解了他们的脾气,那就总结一下,在我们平时设计中如何使用他们。

尽量用同步复位,如果你的规模不是特别大,虽然占有布线资源多一点,但是对系统可靠性还是有帮助的。

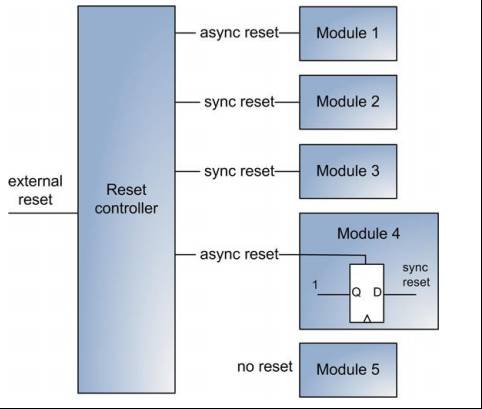

规模很大的时候,可以考虑混和复位方式,在什么场合呢?比如说设计中有多个IP核和功能模块,要求有不同的复位方式,这个时候就要求混和复位方式,另外,还有电路延迟,大型电路中两个模块之间信号延迟可能超过10ns,如果时钟周期为3ns,需要3个时钟周期才能通过,所以,大型设计中完全同步是非常不容易的。如图所示为一个复杂的混和复位树。各种复位都用上了。