上篇介绍了如何利用verilog实现4线SPI配置时序,本篇将以AD9249介绍其3线SPI配置的verilog实现。

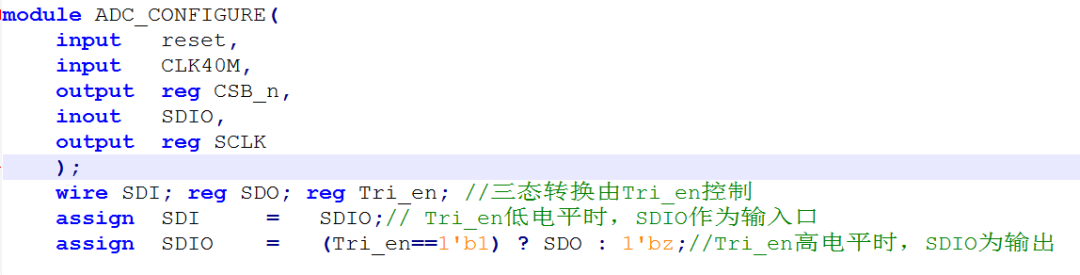

3线SPI的时钟产生方式和上一篇的4线SPI相同,这里不在叙述。两者的不同点在于:三线SPI模式需要FPGA管脚三态控制SDIO的输入/输出状态。下图所示的代码即为三态控制逻辑。SDI、SDO成为了内部逻辑信号,和上篇的4线SPI配置相同操作即可,而SDIO为三态管脚,需定义为inout类型。

Tri_en信号即为三态控制信号,在写操作中,该信号必须置高;然而在读操作中,该信号在写地址的前半段需置高,当完成写地址操作后,ADC的SDIO接口由输入变输出,此时FPGA控制Tri_en信号拉低,将FPGA端的SDIO管脚由输出变为输入,从而正常接收ADC的SDIO口输出的寄存器数值。

Tri_en到底应该在哪个具体时刻拉低,以便完成FPGA的SDIO三态转换呢?答案其实在第三篇已经说的很清楚了~~~~

另外,3线SPI读/写操作有专门的读写标志位,大家务必要留心~

3线SPI的FPGA实现就介绍到这里了,其实和4线基本一样,只不过多了个三态转换而已,大家把上篇的4线SPI的实现过程想清楚了,再加上一个三态转换控制,3线SPI也就拿下了。