SPI是一种全双工的串行通信总线,最早由Motorola提出,虽然应用广泛,但没有一个统一的总线标准。相较于IIC总线,SPI具有通信速度快、协议灵活、无复杂的总线仲裁机制、支持中断等优点,但缺点也很明显。

例如,SPI需要四根线,而IIC只需要两根线;SPI为一主多从的总线架构,从而不会发生抢占总线的情况,所以在I/O电路上,可使用Push-Pull输出,对比IIC的OD门可获得更快的开关速度,但是SPI在发送一帧数据后,会产生中断,中断期间需读取数据寄存器中的数据,否则后续传输的数据会丢失,这就导致在连续传输数据的情况下,SPI的通信速度会受制于中断的处理速度;SPI协议虽然灵活,但是由于缺乏统一定义,各厂商间的兼容性并不强,而且SPI协议缺乏握手以及数据校验机制,主机发出的数据从机并不一定能正确接收,即SPI通信的可靠性不及IIC。

基于以上SPI的基本特性,下文将着重讨论以下几个问题:

- Motorola如何定义SPI总线?

- 为什么SPI的速率可以更快?有什么因素限制了其上限?

- 移位寄存器的原理?

- SPI传输数据的完整过程是怎样的?

Motorala的总线协议

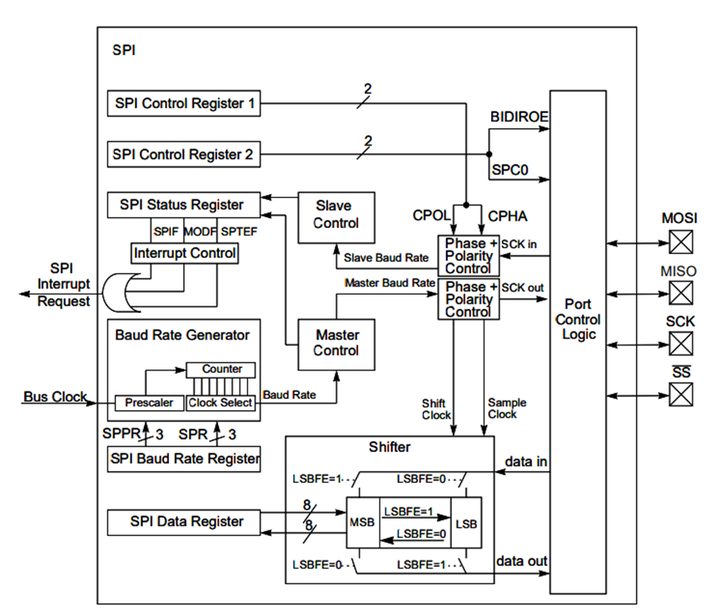

图1 SPI总线模块示意图

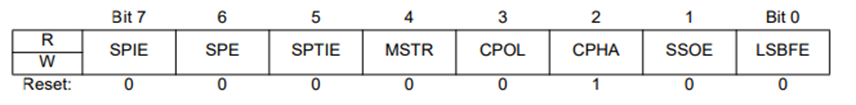

SPI Block Guide给出了SPI的内部模块如图1所示,由图1可知,SPI有4个IO口,分别为时钟线SCK、片选信号SS、主机数据输出MOSI以及主机数据输入MISO。其工作模式通过多个8bit寄存器进行配置,SPICR1(SPI Control Register 1)主要对时钟的有效电平(CPOL)及采样边沿(CPHA)进行配置,当CPOL=1时,表示低电平有效,当CPHA=1时,表示在时钟的偶数沿进行采样(结合CPOL=1的情况,则为上升沿采样)。除此之外,SPICR1还可以对主从选择、中断使能、片选使能以及是否先传输低有效位等进行配置。

图2 SPI控制寄存器1

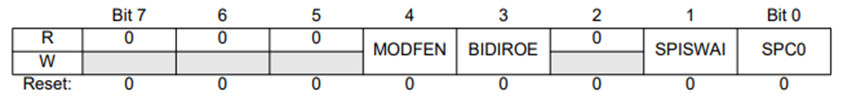

SPICR2(SPI Control Register 2)通过对BIDIROE和SPC0的配置可使能I/O口的双向传输,对SPISWAI的配置可使SPI总线进入等待模式,降低功耗。另外,主机模式下,通过配置该寄存器的MODFEN位,可使其片选无效。

图3 SPI控制寄存器2

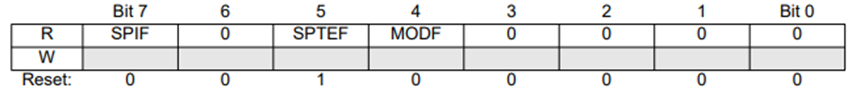

SPISR(SPI Status Register)主要用于指示当前SPI总线的工作状态,SPIF为数据已传入数据寄存器的标识位,当其为1时表示可以从SPI数据寄存器中读取数据,该位可通过读取SPISR清零。SPITEF为发送空标识位,当其为1则表示发送的数据寄存器为空,可写入数据,当其不为1时,对数据寄存器的写入无效。MODF为模式错误标识位,当设备配置为主机且片选有效时该位置1,三者皆可产生中断。

图4 SPI状态寄存器

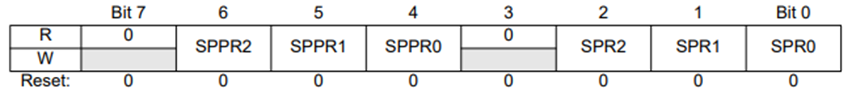

SPIBR(SPI Buard Rate Register)主要用于配置分频系数,对输入时钟进行分频,生成所需频率的工作时钟。

图5 SPI波特率寄存器

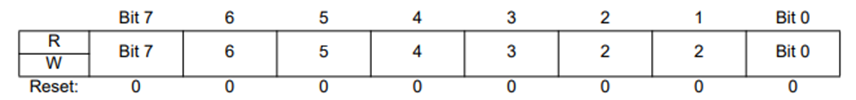

SPIDR(SPI Data Register)分为接收和发送两个Buffer,分别用于接收数据和待发送数据的暂存,工作时,数据寄存器需与移位寄存器配合完成数据的收发。

图6 SPI数据寄存器

此外,该协议将对SPI总线分为运行模式、等待模式和停止模式。其中等待模式和停止模式下,主机都会停止生成时钟和停发数据,从机进入这两种模式则不响应,保持和主机的同步状态,两者的不同在于等待模式有SPICR2的SPISWAI位触发,而停止模式则取决于系统状态,如时钟常0或常1等。

SPI的传输速度及其限制条件

IIC在Ultra-Fast-mode模式下可达到5Mbps的水平,而SPI的总线规范里没有对其传输速率进行说明,根据各厂家的器件手册来看,其通信速率可达到10M以上。值得一提的是,IIC在Ultra-Fast-mode下之所以可以达到5Mbps,是因为其I/O口采用了Push-Pull结构,所以在IIC Ultra-Fast-mode与其他模式不可兼容(否则可能短路)。SPI由于其不像IIC为多主机的总线结构,避免了总线控制权的竞争,所以SPI设备之间不必担心I/O口的短路风险,所以可以使用Push-Pull的结构,从而使发送速度得以提升,IIC在接收侧增加了施密特触发器使边沿更陡峭,从而提升通信速度,SPI的输入电路理论上应存在同样的设计,才能达时通信速度不受掣肘。当然,在I/O口使用同样电路结构的前提下,SPI还能做到比IIC更高的通信速率,说明还有其他因素制约着通信速度的上限。事实上,IIC Ultra-Fast-mode下5Mbps的通信速度只是标准规定的,只要驱动够强、距离缩短(阻抗及总线电容降低)以及硬件电路支持,那么,通信速度的上限是可以突破的。

移位寄存器的原理

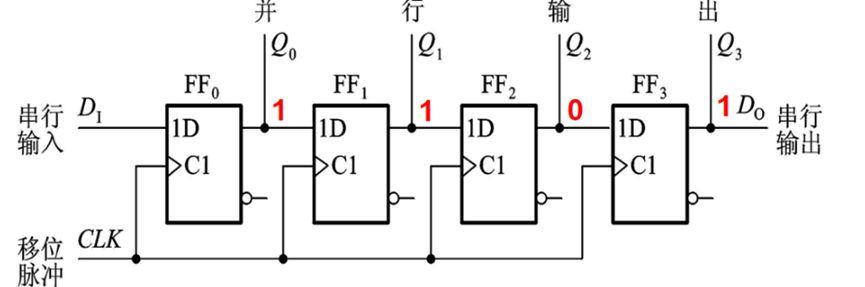

移位寄存器是SPI总线通信系统的重要组成部分,通信过程实际上就是主、从设备移位寄存器里的数据交换。移位寄存器一般由多个D触发器构成,由图7可知,在时钟边沿到达时,寄存器输出端将会刷新数据,那么随着时钟脉冲的到来,数据就可以逐步向高位的寄存器进行移动,最后再并行输出到SPI的数据寄存器中

图7 移位寄存器结构

SPI传输数据的完整过程

SPI的数据寄存器分为发送和接收两个Buffer,在进行数据传输之前,SPISR中的SPTEF位处于置位状态,表示发送寄存器空,控制器读取到该标志位后,将数据写入数据寄存器中,SPI发送数据寄存器将数据写入移位寄存器中,开始一次数据传输过程。SPI是串行通信,每个时钟周期只传输1bit的数据,每次都是主、从机的移位寄存器最高位bit数据被发送,并接收对方发来的数据发到以为寄存器的最低位中。在这个过程中,存在两种不同数据发送和采样模式,一种是在第一个时钟沿发送数据,在第二个时钟沿对数据进行采样,这种方法适用于驱动能力较强的设备,因为其数据的建立时间只有半个时钟周期,若驱动能力不足导致数据上升下降时间较慢,可能会导致数据采样错误。第二种模式是在采样沿后更新数据,这样数据建立时间有近一个时钟周期,较为充裕,通信频率也有所受益。但这也意味着其保持时间较短,因此需对时钟、数据走线进行等长控制,获取一个较低的走线延时,否则也会导致数据采样错误。