- 说明

- 点击数:6681

摘要:1394B总线以其高带宽、低延迟、高可靠特性在机载系统中应用越来越广泛。该文介绍了1394B总线协议,实现了一种智能1394B接口模块,并进行了通信测试,具有一定的参考意义。

关键词:1394B, 通信

1 概述

1394B总线网络与传统1553B总线系统相比具有高带宽、低延迟、高可靠性等方面优势,已经广泛应用于新一代战机的航电系统、飞行器管理系统和机电公共设备管理系统。

2 1394B总线概述

IEEE 1394-1995最初由Apple公司提出,由IEEE正式制定,支持100/200/400Mbps通信速率,其目的是为了简化计算机的外部连线,并且为实时数据传输提供一个高速接口[1]。2000年对IEEE 1394-1995标准进行补充,增强了互操作性,解决了一些二义性问题,形成了IEEE 1394a-2000。2002 年起,对IEEE 1394-1995 规范进行了不断地完善, 确定了IEEE-1349b-2002,其目标是用于传输多媒体数据,其带宽,传输速度,距离等都有了大幅度提高[2]。

1394B总线具有如下特点:

- 采用异步流包:异步流包是异步时间间隔内发送的等时包。异步流被用于网络上大多数的通信。

- 使用STOF同步:STOF包由每条总线上的CC按照固定的帧速率发送STOF包通知总线上所有的节点新的一帧开始。通过传输一个固定速率的STOF包实现网络的同步。

- 纵向奇偶校验(VPC):纵向奇偶校验(VPC)是作为1394物理层产生的CRC校验的一个附加校验。VPC提供物理层和软件层在进行消息传输过程中的附加数据完整性的保障。

- 通道号静态分配:因为异步流包在格式上与等时包一致,所以也由通道号来确定目标节点,总线上每个节点的通道号是由应用预先分配的,根据体系结构而定。

- 带宽预分配:每一帧开始后(STOF包),总线上每个节点的发送和接收的时间由应用根据体系结构预先分配。

- 使用匿名签署协议(ASM):匿名签署协议是为了满足嵌入式实时系统需求的上测试协议,ASM协议建立于下层协议,不需要1394消息头传输ASM特殊消息[3]。

3 模块设计

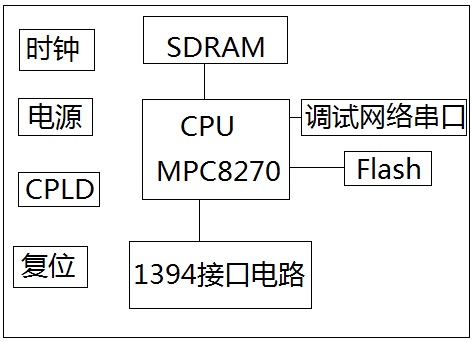

智能1394B接口采用MPC8270实现,对外提供三个1394B端口。模块主要由时钟电路,电源电路,复位电路,1394接口电路以及处理器电路组成。系统结构如图1所示。

图1 系统结构

3.1 处理器电路

处理器电路主要由处理器,SDRAM,CPLD和FLASH组成。

- 说明

- 点击数:3131

1 引 言

列车需要传输大量的设备控制和旅客服务信息,随着这些信息的数量和种类不断地增长,迫切需要一种大容量,高速度的信息传输系统。为此,国际电工委员会(IEC)制定了一项用于规范车载设备数据通信的标准——IEC61375(列车通信网标准),即TCN标准,该标准于1999年6月成为国际标准。目前国际上主要的TCN产品供应商是德国西门子和瑞士Duagon公司,国内的株洲电力机车研究所和大连北车集团电力牵引研究所等单位进行了大量的TCN相关研究工作并取得了丰硕的科研成果。

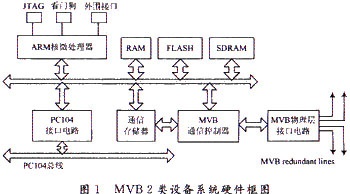

TCN标准推荐在机车上层使用绞线式列车总线WTB,在下层使用多功能车辆总线MVB。MVB总线和机车中的各种电气设备相连,这些设备按性能可以分为5类,其中二类设备的主要特征是具有消息数据通信的功能。为了实现消息数据通信,需要在实时操作系统的支持下采用软件编程,利用应用程序接口API等接口来调用网络协议的各种功能,从而实现消息数据的通信。MVB 2类设备硬件核心采用ARM7内核微处理器NET+50作为主CPU实现系统的总体控制,采用MVBC01芯片作为MVB通信控制器实现链路层的数据处理,软件核心采用嵌入式实时操作系统Nucleus Plus来实现任务管理、中断管理等上层管理。

2 MVB 2类设备系统硬件设计

硬件系统设计主要包括应用处理器模块、通信存储器模块、通信控制器模块、存储器模块、PC104接口模块、物理层接口模块等几部分的设计,其中核心模块是ARM处理器和MVB通信控制器MVBC01。系统硬件设计框图如图1所示。

系统硬件各部分电路的功能和设计方法如下:

2.1 应用处理器模块

应用处理器采用ARM核微处理器NET+50作为核心处理器。NET十50由Netsilicon公司生产,属于ARM7系列。NET+50处理器包括一个ARM7TDMI核,32位内部总线,支持所有SRAM,SDRAM,FLASH,E2PROM,有40个可编程I/O接口引脚,16个输入接口引脚,36个可编程中断,2个完全独立的HDLC/UART/SPI串行口以及完整的以太网控制器。

- 说明

- 点击数:4154

一、按顺序安装好Tornado的几张盘后。打开控制台先后输入如下:

C:\Tornado2.2\host\x86-win32\bin>torvars.bat (此为设置系统环境变量的批处理)

C:\Tornado2.2\target\src>make CPU=PENTIUM4 TOOL=gnu SNMPV3=ON AGENTX=ON rclean (清理中间文件)

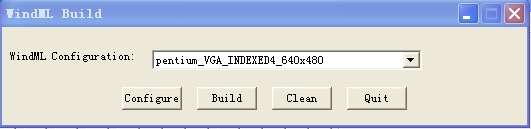

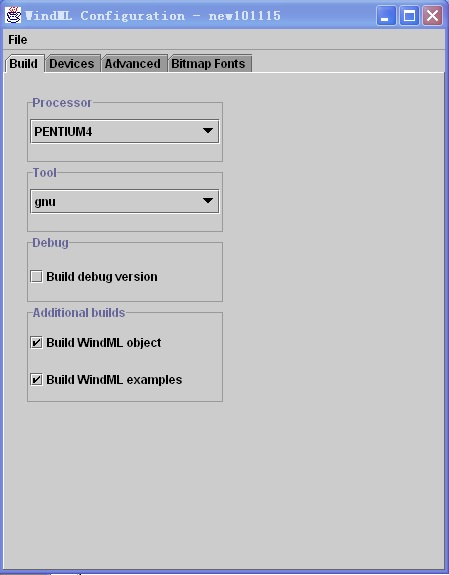

二、编译设置WindML

打开Tornado菜单Tool -> WindML 打开了WindML Build对话框

选择pentium_VGA_INDEXED4_640×480

点击configure按钮进行设置

各个选项设置如下:

- 说明

- 点击数:4493

摘要:简要的介绍了MVB总线及多功能车辆总线控制器芯片(MVBC)的功能和结构,以及帧收发器在MVBC中的重要作用;详细论述了帧收发器中曼彻斯特编码、译码器的设计,CRC校验电路的电路设计,以及负责帧发送、接收的Encoder模块、Decoder模块的设计实现;最后介绍了该模块的验证方案。

关键词: MVB; WTB; MVBC; CRC; 曼彻斯特码

1 前言

随着嵌入式微机控制技术和现场总线技术的发展,现代列车的过程控制已从集中型的直接数字控制系统发展成为基于网络的分布式控制系统。基于分布式控制的MVB(多功能车辆总线)是IEC61375-1(1999)TCN(列车通信网络国际标准)的推荐方案,它与WTB(绞线式列车总线)构成的列车通讯总线具有实时性强、可靠性高的特点。列车车辆的现代化的发展趋势与可靠性、安全性、通讯实时性的要求使MVB逐渐成为下一代车辆的通讯总线标准。

MVB是主要用于有互操作性和互换性要求的互联设备之间的串行数据通讯总线,除用于车辆通讯,也可用作其它现场总线。

MVB与MVBC密不可分,MVBC(多功能车辆总线控制器)是MVB总线上的新一代核心处理器,它独立于物理层和功能设备,为在总线上的各个设备提供通讯接口和通讯服务。MVBC与上一代MVB通信控制器BAP15-2/3在性能上有了很大的提高,是目前MVB总线上最先进的通信控制器。

MVB总线通过总线适配器与MVBC相连,根据IEC-61375,MVB总线上采用曼彻斯特码,并每64位帧数据后加以8位CRC校验码。MVB的帧分为主帧和从帧,分别由帧头、数据、校验码以及帧尾构成,不同帧的类型通过帧头来判别。

MVB与MVBC之间数据通信在MVBC中由帧收发器来完成,包括帧的发送接收控制、曼彻斯特编解码以及CRC校验码的产生与数据校验。帧收发器在MVBC中起着数据链路层的底层数据处理的作用,是MVBC芯片的设计难点之一,该模块的设计实现对于整个MVBC的开发有着重要的作用。

本文主要介绍位于MVBC总线物理层接口的帧收发器模块的算法和实现方法。

2 MVBC简介

MVBC可通过配置应用在IEC.TCN标准的Class1,2,3,4设备当中。总线连接可编程车载电子设备,也连接一些简单的传感器及执行机构,最多可寻址4096个设备。

MVBC把来自于MVB总线的串行化信号转换为并行的数据字节,也把需发送的字节交由串行化电路发送到传输介质上。MVBC可根据配置实现总线主与总线从的功能,实现数据链路层以及一部分传输层的数据处理,并通过通讯存储器来与上层软件交互。总线控制器内部包含编码/译码电路和控制通信存储器所需的逻辑电路,用来控制帧的发送和接收(如冲突检测、帧的前导比特处理、CRC校验位的处理等);对输入帧译码并检验其有效性;把数据存放到相应的通信存储器中。

图2-1:MVBC结构框图

- 说明

- 点击数:3153

车辆显控系统是对车辆工作状态信息进行显示、控制,并完成人机交互的系统。车辆显控系统需要在显示文字、图形和视频的同时响应按键操作,并对车辆控制系统进行操控。这就要求系统具有实时响应、并行处理多个任务的能力。本文在以PowerPC MPC8548E为处理器的控制主板上应用实时操作系统VxWorks,实现了实时响应系统操作、显示相应信息的功能。以此主板为核心控制主板的显控系统,具有高性能、高稳定性和良好的兼容性。

1 PowerPC MPC8548及其控制主板概述

PowerPC MPC8548是Freescale公司开发的新一代PowerQUICC III系列的高性能处理器。其内部工作频率可达1.33 GHz,在该工作频率上处理性能可达3065 MIPS。一级缓存有指令缓存和数据缓存各32 KB,二级缓存为512 KB,支持DDR1和DDR2存储器控制器,支持PCI、PCIX和PCIE接口,支持SRapid IO接口和4个GbE接口。MPC8548不仅拥有强大的数据处理能力,还具有很强的通信处理能力,可靠性高,抗恶劣环境能力好,特别适合对网络性能要求较高及有多个接口的场合。

车辆显控系统的核心控制主板是以PowerPC MPC8548E为处理器的嵌入式系统。该系统通过扩展显示器、内存、Flash存储器以及其他接口控制电路,构成了高性能、高可靠性的核心控制主板。以此控制主板为硬件平台,移植嵌入式实时操作系统VxWorks,对接口设备驱动进行二次开发,继而以VxWorks为软件开发平台,开发应用程序,实现显示和控制任务。

2 PowerPC控制主板硬件设计

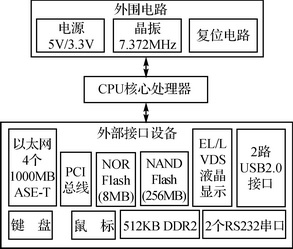

如图1所示,PowerPC控制主板硬件系统由处理器、外围电路和外部接口设备组成。外围电路包括电源、晶振和复位电路;外部接口电路包括串口、网口、EL/LVDS液晶显示、16位PCI总线、USB接口、Flash、鼠标和键盘等。

图1 PowerPC控制主板硬件结构图

3 PowerPC控制主板软件设计

© 2026 VxWorks Club