# RT Embedded http://www.kontronn.com

## USB 3.0 中的 CRC 校验原理及实现

王良俊,马 琪

(杭州电子科技大学 微电子 CAD 研究所, 浙江 杭州 310037)

摘 要:循环冗余码(CRC)是 USB 协议中重要的错误检测措施。在此分析了 USB 3.0 数据包的基本格式以及 USB 3.0 协议中 CRC 校验的特点,针对 USB 3.0 数据高速传输的要求,设计实现并行发送端 CRC 产生和接收端 CRC 校验电路,功能仿真结果证明了其有效性。

关键词:USB 3.0; CRC 校验; Verilog HDL 代码; 仿真结果

中图分类号: TN919-34 文献标识码: A 文章编号:1004-373X(2011)18-0170-02

#### CRC Principle and Its Design in USB3.0

WANG Liang-jun, MA Qi

(Microelectronics CAD Research Institute, Hangzhou Dianzi University, Hangzhou 310037, China)

Abstract: CRC is an important error detection measure which protects over control and data fields in USB specification. The basic packet format and characteristics of CRC computation in USB3.0 are analyzed. The parallel circuits of CRC generation in transmitter and CRC detection in receiver are designed, which can detect whether the packets in the event of damage during transport. At last, Simulation results prove its validity. Compared with traditional serial circuit, the parallel circuit for which the clock frequency can be reduced, the circuit can be achieved easily and the power consumption can be significantly reduced.

Keywords: USB3.0; CRC; Verilog HDL code; simulation resutts

在通用串行总线(USB)的数据传输过程中,数据循环冗余校验(CRC)[1]是为了保证数据传输中数据的正确性而采用的数据保护方法。USB 3.0 协议中为了检测和减少这类错误,一方面提供了一系列硬件和软件措施,以保证数据传输的正确性;另一方面在每个包中加入检测位来发现这些瞬时的错误。协议中对每个包的控制位和数据位提供了循环冗余校验,若出现了循环冗余码的错误,则认为该包已经损坏[2-3]。

本文介绍了 USB 3.0 设备控制器中的协议层在数据收发时,如何采用并行电路来完成数据包发送时 CRC 码的产生和接收时 CRC 码的校验,并行处理方法与常用的串行处理相比,极大地降低了功耗和电路综合的难度<sup>[4]</sup>。

#### 1 USB 3.0 中的 CRC 校验

USB 3.0 协议规定了 4 种类型的包<sup>[5]</sup>:链路管理包(LMP),传输包(TP),数据包(DP)和同步时间戳包(ITP)。链路管理包(LMP)只遍历直接连接的端口,主要用于管理该连接。传输包遍历主机和设备路径中的所有链路,用来控制数据包流,配置设备和集线器等,传输包没有数据部分。数据包遍历主机和设备路径中的所有连接。同步时间戳包是一个多播数据包,由主机发

送到所有激活的连接。

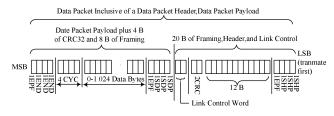

USB 对所有传输数据的保护采用了 CRC 校验和数据重传的方式。当通过检错码判断错数据包错误时,发送端通过重发来达到纠错的目的。USB 3.0 数据包由数据包头(DPH) 和数据包有效载荷(DPP) 两部分组成,DPH 类似于一个传输包,DPP 中有一个 32 位 CRC (CRC-32),可以确保数据的完整性。数据包以 16 B 的数据包头开始(有的包只有包头没有数据部分),包头含了如何处理该包的信息。一个完整的 USB 3.0 数据包的格式如图 1 所示。

图 1 完整数据包格式

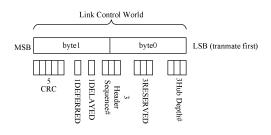

在数据包头(DPH)中,有一个长度为 2 字节 16 位的 CRC 校验码对数据包头的 12 个字节信息进行保护。在数据部分(DPP)中,包含最大 1 024 B 的数据,有一个长度为 4 B 32 b 的 CRC 校验码对数据部分进行保护。另外,在数据包头中,有 2 B 的链接控制字(Link Control Word),其中长度为 5 位的 CRC 用来对链接控制字中其他的 11 位信息进行保护,格式如图 2 所示。

## RT Embedded http://www.kontronn.com

图 2 链接控制字格式

在 USB 3.0 协议中, CRC 校验有以下特点:

- (1) 在发送端, CRC 校验在初始状态时将余数寄存器的值置为全 1,如果没有这样的预设置,就不能正确地保护数据包开始为 0 的数据位。在接收端,也同样将移位寄存器预设为全 1 状态,以保证接收到的被除数加上一个相同的常数,如果数据传输无误,则余数产生器应该得到相同的余数。

- (2) 采用了 3 种类型的 CRC 校验:5 位、16 位和 32 位CRC 校验。5 位 CRC 校验采用的生成多项式为:  $G(X) = X^5 + X^2 + 1$ , 如果准确无误地接收到数据,接收端的 5 位余数应该是 01100;16 位 CRC 校验采用的生成多项式为:  $G(X) = X^{16} + X^{15} + X^2 + 1$ , 接收端的 16 位余数应该是 10000000000001101;32 位 CRC 校验采用的生成多项式为:  $G(X) = X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X^1 + 1$ , 接收端中的 32 位余数应该是 32 HC704DD7B。

- (3) 发送端对输入的数据作除法运算后,将所得到的余数按位取反,取反后的余数放在待发送数据的高位,组成了新的数据流。接收端 CRC 校验采用与 CRC 产生相同的算法来实现,只是作为输入数据的是原始的被除数数据和对应的 CRC 校验码组成的新数据流。如果接收端的余数与(2)的要求一致,则说明接收端准确无误地接收到了数据。

#### 2 并行 CRC 校验的设计[6-7]

在 USB 3.0 协议中,数据最高传输速率高达 5 Gb/s,串行方法无法满足实时性要求。本文中,CRC 校验采用的是并行设计方法。

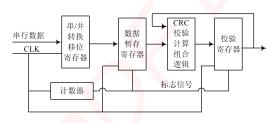

在 USB 3.0 协议中,数据收发是以字节为单位来传输的,所以在发送端和接收端可以通过一个 8 位移位寄存器将串行数据转换成字节表示形式,然后再对数据进行并行的 CRC 码产生和校验。

以链接控制字中的 5 位 CRC 为例,发送端并行 CRC 产生的设计结构如图 3 所示。计数器用于产生标志信号,计数值为 8 时串并转换结束,数据暂存寄存器获取字节数据,经组合逻辑计算后产生新的校验寄存器值。并行 CRC5 的余数多项式表达式如下:

crc\_d[0] < = hold[6]^hold[5]^hold[3]^hold[0]^crc\_d[0]^

crc\_d[2]^crc\_d[3];</pre>

crc\_d[1] < = hold[7]^hold[6]^hold[4]^hold[1]^crc\_d[1]^ crc\_d[3]^crc\_d[4];

$\begin{array}{l} crc_d[2] < = hold[7]^hold[6]^hold[3]^hold[2]^hold[0]^c \\ crc_d[0]^crc_d[3]^crc_d[4]; \end{array}$

crc\_d[3] < = hold[7]^hold[4]^hold[3]^hold[1]^crc\_d[0]^

crc\_d[1]^crc\_d[4];</pre>

$crc_d[4] < = hold[5]^hold[4]^hold[2]^crc_d[1]^crc_d[2];$

图 3 发送端并行 5 位 CRC 产生的结构

在接收端,按照和发送端同样的电路,对发送端产生的 CRC 校验码和输入的数据一并进行 CRC 校验,如果接收端成功接收,最后得到的 CRC 校验码为常数(01100)。

#### 3 仿真结果

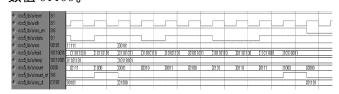

发送端和接收端的并行 CRC 产生和校验设计用 Verilog HDL 实现,用 Model Sim 工具进行仿真,发送端并行 CRC 产生和接收端 CRC 校验的仿真波形分别如图 4 和图 5 所示。在发送端,每输入 8 个数进行一个并行的 CRC5 计算,erc\_d 寄存器的值随发送的数不断更新,直到最后产生一个余数,在接收端将该余数和发送端的数一并进行 CRC5 校验,最后 CRC 得到一个常数值 01100。

图 4 发送端并行 CRC 产生的仿真波形图

图 5 接收端并行 CRC 校验的仿真波形图

#### 4 结 语

虽然并行方法在电路规模上比串行算法大,但是能够在单位时间内完成更多位数据的校验,可以有效降低电路的工作频率,硬件实现也较容易。USB 3.0 数据的最高传输速率高达 5 Gb/s,采用并行 CRC 校验设计

(下转第 174 页)

## RT Embedded http://www.kontronn.com

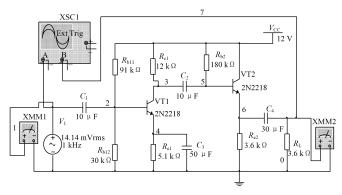

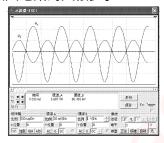

察到 ¼ 和 ¼ 的波形如图 8 所示。

此时测得  $U_i = 14.14 \text{ mV}$ ,  $U_0 = 1.788 \text{ V}$ ,  $A_u = U_0 / U_i = -1.788 \text{ V}$  / 14.14 mV = -126。

图 6 两级阻容耦合放大电路的仿真电路

由图 8 可以看出, u<sub>0</sub> 的波形没有明显的非线性失真,而且 u<sub>1</sub> 和 u<sub>0</sub> 的相位相反。另外可以看出,两级放大电路的放大倍数比单管放大电路的大很多。

图 8 两级放大电路 的 u<sub>i</sub> 和 u<sub>o</sub> 的波形

#### 2 结 语

用 Multisim 10 软件进行建模、仿真,通过在元器

(上接第 171 页)

完成 USB 3.0 数据传输中 CRC 码的产生和校验。可使高速 USB 串行接口引擎电路方便地与 UTMI接口。

#### 参考文献

- [1] 张爱丽. USB 2.0 主机控制器内核 SIE 的设计[D]. 广州: 暨南大学,2006.

- [2] ADERSON Don. USB 系统体系[M]. 2 版. 北京:中国电力 出版社 2007

- [3] 郭熙业,苏绍璟,王跃科.并行 CRC-32 校验码生成算法研究及其实现[J]. 计算机技术与应用,2008(5):1-2.

- [4] 王成儒,李英伟. USB2.0 原理与开发[M]. 北京:国防工业

件栏和仪器仪表栏中选择合适的元器件和仪表,设置属性并在面板上合理的调整各个元器件的方向位置构建仿真电路,仿真电路生成直观、简单,还可以随时改变参数,并用示波器随时观察仿真波形,使得仿真更具有实时性、直观性。本文应用 Multisim 10 软件对单管共射放大电路和阻容耦合放大电路进行虚拟电子技术实验,可以十分方便快捷地获取实验数据。结果表明仿真与理论分析和计算结果一致,突破了传统实验中硬件设备条件的限制,大大提高了实验的深度和广度。

#### 参考文献

- [1] 杨素行. 模拟电子技术基础简明教程[M]. 北京:高等教育出版社,2006.

- [2] 童诗白. 模拟电子技术基础[M]. 北京: 高等教育出版 社,2006.

- [3] 康华光. 电子技术基础模拟部分[M]. 北京:高等教育出版 社,2006.

- [4] 崔文华. 基于 Multisim 10 的高频调谐放大电路[J]. 机电工程,2010,27(2):19-21.

- [5] 熊旭军. 基于 Multisim 的差分放大电路仿真分析[I]. 现代电子技术,2009,32(4):109-112.

- [6] 聂典,丁伟. Multisim 10 计算机仿真在电子电路设计中的应用[M]. 北京:电子工业出版社,2009.

- [7] 崔建明,陈惠英,温卫中.电路与电子技术的 Multisim 10 仿 真[M].北京:中国水利水电出版社,2009.

- [8] 李冬生.LDA 仿真与虚拟仪器技术[M]. 北京:高等教育出版社,2004.

- [9] 崔霞,魏鲁原. Multisim 10 在电子技术实习中的应用[J]. 实验科学与技术,2010(8):7-9.

出版社,2004.

- [5] 张文豪,王春梅,姚秀娟.可配置 m 序列并行生成算法研究 [J]. 微计算机信息,2008,24(7):65-67.

- [6] 王福昌,熊兆飞,黄本雄.通信原理[M].北京:清华大学出版社,2006.

- [7] Intel Corporation. Universal serial bus3.0 specification[M]. Revision1.0. [S.1.]: Intel corporation, 2008.

- [8] 王金明. 数字系统设计与 Verilog HDL[M]. 2 版. 北京:电子工业出版社,2006.

- [9] 夏宇闻. Verilog 数字系统设计[M]. 2 版. 北京:北京航空航天大学出版社.2008.

- [10] 林丰成,竺红兰,李立.数字集成电路设计与技术[M].北京:科学出版社,2008.

作者简介:王良俊 男,杭州电子科技大学微电子 CAD 研究所研究生。研究方向为集成电路设计与 EDA 技术。

## 嵌入式资源免费下载

## 总线协议:

- 1. 基于 PCIe 驱动程序的数据传输卡 DMA 传输

- 2. 基于 PCIe 总线协议的设备驱动开发

- 3. CANopen 协议介绍

- 4. 基于 PXI 总线 RS422 数据通信卡 WDM 驱动程序设计

- 5. FPGA 实现 PCIe 总线 DMA 设计

- 6. PCI Express 协议实现与验证

- 7. VPX 总线技术及其实现

- 8. 基于 Xilinx FPGA 的 PCIE 接口实现

- 9. 基于 PCI 总线的 GPS 授时卡设计

- 10. 基于 CPCI 标准的 6U 信号处理平台的设计

- 11. USB30 电路保护

- 12. USB30 协议分析与框架设计

### VxWorks:

- 1. 基于 VxWorks 的多任务程序设计

- 2. 基于 VxWorks 的数据采集存储装置设计

- 3. Flash 文件系统分析及其在 VxWorks 中的实现

- 4. VxWorks 多任务编程中的异常研究

- 5. VxWorks 应用技巧两例

- 6. 一种基于 VxWorks 的飞行仿真实时管理系统

- 7. 在 VxWorks 系统中使用 TrueType 字库

- 8. 基于 FreeType 的 VxWorks 中文显示方案

- 9. 基于 Tilcon 的 VxWorks 简单动画开发

- 10. 基于 Tilcon 的某武器显控系统界面设计

- 11. 基于 Tilcon 的综合导航信息处理装置界面设计

- 12. VxWorks 的内存配置和管理

- 13. 基于 VxWorks 系统的 PCI 配置与应用

- 14. 基于 MPC8270 的 VxWorks BSP 的移植

## Linux:

- 1. Linux 程序设计第三版及源代码

- 2. NAND FLASH 文件系统的设计与实现

- 3. 多通道串行通信设备的 Linux 驱动程序实现

- 4. Zsh 开发指南-数组

- 5. 常用 GDB 命令中文速览

- 6. 嵌入式 C 进阶之道

### Windows CE:

- 1. Windows CE. NET 下 YAFFS 文件系统 NAND Flash 驱动程序设计

- 2. Windows CE的 CAN 总线驱动程序设计

- 3. 基于 Windows CE. NET 的 ADC 驱动程序实现与应用的研究

- 4. 基于 Windows CE. NET 平台的串行通信实现

- 5. 基于 Windows CE. NET 下的 GPRS 模块的研究与开发

- 6. win2k 下 NTFS 分区用 ntldr 加载进 dos 源代码

- 7. Windows 下的 USB 设备驱动程序开发

- 8. WinCE 的大容量程控数据传输解决方案设计

- 9. WinCE6.0 安装开发详解

- 10. DOS 下仿 Windows 的自带计算器程序 C 源码

- 11. G726 局域网语音通话程序和源代码

- 12. WinCE 主板加载第三方驱动程序的方法

- 13. WinCE 下的注册表编辑程序和源代码

- 14. WinCE 串口通信源代码

- 15. WINCE 的 SD 卡程序[可实现读写的源码]

## PowerPC:

- 1. Freescale MPC8536 开发板原理图

- 2. 基于 MPC8548E 的固件设计

- 3. 基于 MPC8548E 的嵌入式数据处理系统设计

- 4. 基于 PowerPC 嵌入式网络通信平台的实现

- 5. PowerPC 在车辆显控系统中的应用

6. 基于 PowerPC 的单板计算机的设计

### ARM:

- 1. 基于 DiskOnChip 2000 的驱动程序设计及应用

- 2. 基于 ARM 体系的 PC-104 总线设计

- 3. 基于 ARM 的嵌入式系统中断处理机制研究

- 4. 设计 ARM 的中断处理

- 5. 基于 ARM 的数据采集系统并行总线的驱动设计

- 6. S3C2410 下的 TFT LCD 驱动源码

- 7. STM32 SD 卡移植 FATFS 文件系统源码

- 8. STM32 ADC 多通道源码

- 9. ARM Linux 在 EP7312 上的移植

## Hardware:

- 1. DSP 电源的典型设计

- 2. 高频脉冲电源设计

- 3. 电源的综合保护设计

- 4. 任意波形电源的设计

- 5. 高速 PCB 信号完整性分析及应用

- 6. DM642 高速图像采集系统的电磁干扰设计

WeChat ID: kontronn